- Produkte

-

Technologien

- IR LayerRelease™ Technology

- MLE™ - Maskless Exposure Technologie

- Nanopräge-Lithographie (NIL) - SmartNIL®

- Wafer-Level Optics

- Optische Lithographie

- Fotolackverarbeitung

- Temporäres Bonden und De-Bonden

- Eutektisches Bonden

- Transient Liquid Phase (TLP) Bonden

- Anodisches Bonden

- Metall-Diffusionsbonden

- Hybrid- und Fusionsbonden

- Die-to-Wafer Fusion and Hybrid Bonding

- ComBond® Technologie

- Metrologie

- Unternehmen

- Karriere

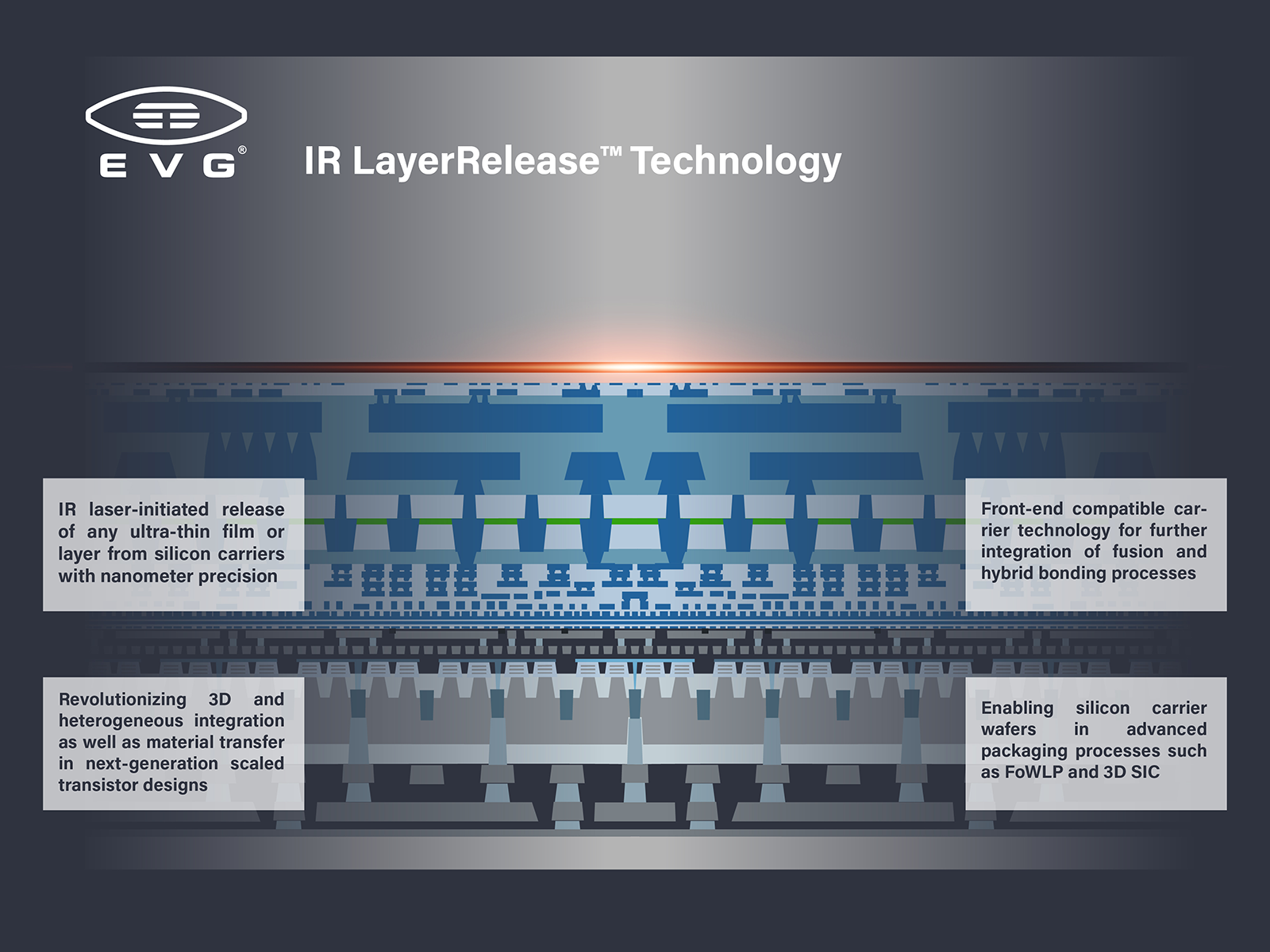

IR LayerRelease™ Technology

IR LayerRelease™ Technology enables nanometer-precision layer transfer through silicon, eliminating glass substrates for advanced packaging and enabling thin-layer 3D stacking

Introduction

EVG's IR LayerRelease Technology is a fully front-end-compatible layer release technology that features an infrared (IR) laser that can pass through silicon, which is transparent to the IR laser wavelength. Coupled with the use of specially formulated inorganic layers, this technology enables an IR laser-initiated release of any ultra-thin film or layer from silicon carriers with nanometer precision.

IR LayerRelease Technology enables silicon wafer carriers in advanced packaging processes such as Fan-out Wafer-level Packaging (FoWLP) using mold and reconstituted wafers as well as interposers for 3D Stacked ICs (3D SIC). At the same time, its compatibility with high-temperature processes enables completely novel process flows for 3D IC and 3D sequential integration applications – enabling hybrid and fusion bonding even of ultra-thin layers on silicon carriers, thereby revolutionizing 3D and heterogeneous integration as well as material transfer in next-generation scaled transistor designs.

Silicon Carriers Benefit 3D Stacking and Back-end Processing

In 3D integration, carrier technologies for thin-wafer processing are key to enabling higher performance systems with increasing interconnection bandwidth. Glass carriers have become an established method for building up device layers through temporary bonding with organic adhesives, using an ultraviolet (UV) wavelength laser to dissolve the adhesives and release the device layers, which are subsequently permanently bonded onto the final product wafer. However, glass substrates are difficult to process with semiconductor fab equipment that have been designed primarily around silicon, and that require costly upgrades to enable glass wafer processing. In addition, organic adhesives are generally limited to processing temperatures below 300°C, which limits their use to back-end processing.

Enabling silicon carriers with inorganic release layers avoids these temperature and glass carrier compatibility issues. In addition, the nanometer precision of IR laser-initiated separation opens up the possibility of processing extremely thin device wafers without changing processes of record. Subsequent stacking of such thin device layers enables higher bandwidth interconnects and opens up new opportunities to design and segment dies for next-generation high-performance systems.

Next-generation Transistor Nodes Demand Novel Layer-transfer Processes

At the same time, transistor roadmaps for the sub-3-nm node are calling for new architectures and design innovations such as buried power rails, backside power delivery networks, complementary field-effect transistors (CFETs) and even 2D atomic channels, all of which will require layer transfer of extremely thin materials. Silicon carriers and inorganic release layers support process cleanliness, material compatibility and high processing temperature requirements for front-end manufacturing flows. However, until now, silicon carriers had to be completely removed using grinding, polishing and etching processes, which results in micron-range variations across the surface of the working device layer, making this method unsuitable for thin-layer stacking at advanced nodes.

EVG’s new technology utilizes an IR laser and inorganic release materials to enable laser debonding on silicon with nanometer precision. This eliminates the need for glass substrates for advanced packaging, avoiding temperature and glass carrier compatibility issues, and enables the ability to transfer ultra-thin (single micron and below) layers via carriers in front-end processing without changing the processes of record. The nanometer-precision of EVG’s new process supports advanced semiconductor device roadmaps calling for thinner device layers and packages, increased heterogeneous integration, and reduced processing costs through thin-layer transfer and the elimination of glass substrates.

Using EVG’s IR LayerRelease technology, the backside of the silicon wafer is exposed with an IR laser, which utilizes a unique wavelength that silicon is transparent to. An inorganic release layer that is pre-built into the silicon stack through standard deposition processes absorbs the IR light, resulting in the separation of the silicon at a predetermined and precisely defined layer or area. The ability to use inorganic release layers enables more precise and thinner release layers to be used (in the range of a few nanometers versus a few microns for organic adhesives). In addition, the inorganic release layers are compatible with high-temperature processing (up to 1000 °C), enabling layer transfer for many new front-end applications, such as epitaxy, deposition and annealing, where organic adhesives are incompatible.

Features

-

3D Integration | Scaling Roadmap:

- Scalpel-like precision of IR laser triggered film release through silicon wafers

- Enables novel, revolutionary 3D integration process flows for ultra-thin layer stacking by fusion and hybrid bonding

- Integrates with any hybrid and fusion bonding process combination for advanced device manufacturing and 3D stacking

- Use of existing FEOL materials, processes and infrastructure

- Transfer layer uniformity is defined by epitaxy uniformity eliminating uniformity limitations from standard wafer thinning processes such as wafer grind, polish and etching

- Universal material transfer in combination with fusion bonding of III-Vs, 2D materials, superlattices, etc.

-

Heterogeneous Integration:

- Enabling silicon carrier wafers as temporary carriers

- Enables use of standard and established process technology, eliminating the need for adapted low temperature processes due to carrier triggered temperature limitations

- Enables Processing of ultrafine pitch redistribution layer patterning on silicon substrates with leading lithography methods

- No need for costly equipment updates or backside deposition to enable glass wafer processing and chucking

Related downloads

Related products

Talk to our EVG technology experts!

Questions?

Events

ICEP 2025

Listen to our talks "Wafer Bonding Advances & 3D Applications" held by our Representative Director Hiroshi Yamamoto on 9:30 Wednesday, April 16 / Room B and "Hybrid Bonding for Heterogenous Integration" held by our Process Technology Manager Europe Gerald Mittendorfer on 12:40 Friday, April 18 / Room A.

JFS Conference and Compoundsemiconductor Industry Expo 2025

Besuchen Sie unseren Stand #A308

MicroNanoFabrication Annual Review Meeting 2025

Besuchen Sie unseren Stand auf dem MicroNanoFabrication Annual Review Meeting 2025!

Share this page with your colleagues on LinkedIn

- IR LayerRelease™ Technology

- MLE™ - Maskless Exposure Technologie

- Nanopräge-Lithographie (NIL) - SmartNIL®

- Wafer-Level Optics

- Optische Lithographie

- Fotolackverarbeitung

- Temporäres Bonden und De-Bonden

- Eutektisches Bonden

- Transient Liquid Phase (TLP) Bonden

- Anodisches Bonden

- Metall-Diffusionsbonden

- Hybrid- und Fusionsbonden

- Die-to-Wafer Fusion and Hybrid Bonding

- ComBond® Technologie

- Metrologie

Questions about our technologies?

Contact the EVG experts