今日、ヘテロ集積化は、スケーリング則にとらわれずに、より高いコンピューティング・パフォーマンスや各種のデバイス性能の向上を実現する為の新たな手法としてますます注目されています。 チップレットデザインの継続的な進化とそのシリコンやパッケージ基板への実装は、パターニング方法を適応させる事で可能となります。 半導体業界が描く集積化に対するこの新しいビジョンにおいては、従来のバックエンドリソグラフィ技術では実現しきれなかった新たなデザインスキームに、迅速に対応できる量産向けの新たな設備が求められます。 さらに、様々なチップデザインに必要なマスクにかかる継続的なコストの上昇と在庫管理にかかる経費は、開発や生産にかかる総コストの中でもかなりの割合を占めています。EV Groupが開発したMLE技術は、マスクに関わる課題やコストの問題を解決し、量産分野における設計の柔軟性と開発サイクルの短縮といった重要な要件に応えます。 さらに、この技術を使用することによって、ほとんどの場合外部委託されているマスク製造が不要となるため、機密性の高いデザインやレイアウトを社外に持ち出す必要がなくなります。この革新的な“デジタルリソグラフィ”技術は、R&Dから生産へ移管する際に生じるギャップを解消するとともに、ダイレベルとウェーハレベルの同時設計を可能にするスケーラブルなソリューションを提供し、先端パッケージングだけでなく、MEMS、バイオメディカル、HDIプリント回路基板製造などのさまざまな市場で求められる厳しい要求に応えます。

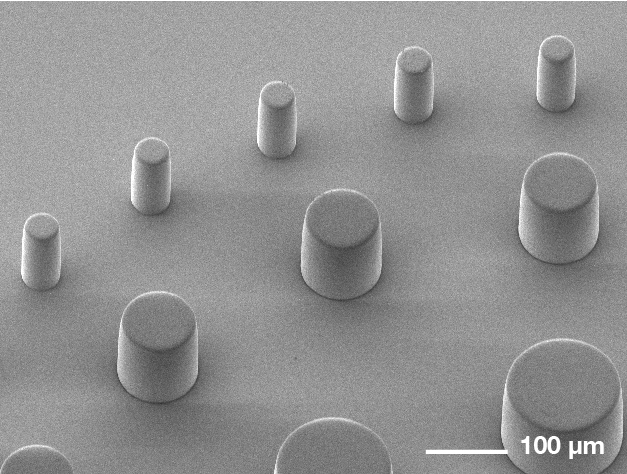

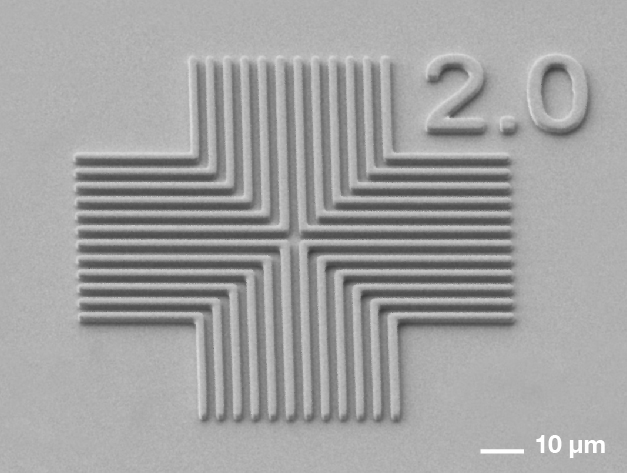

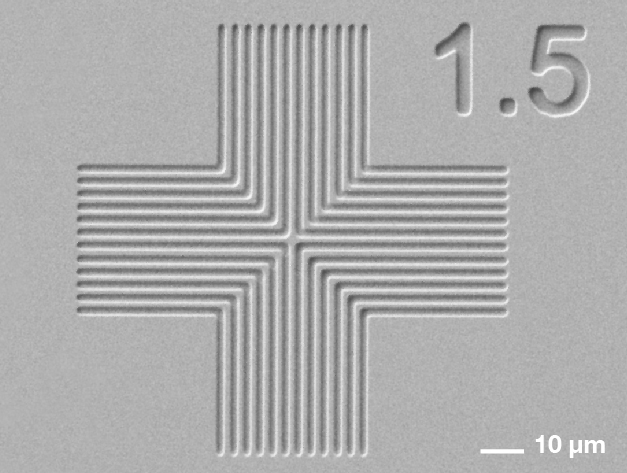

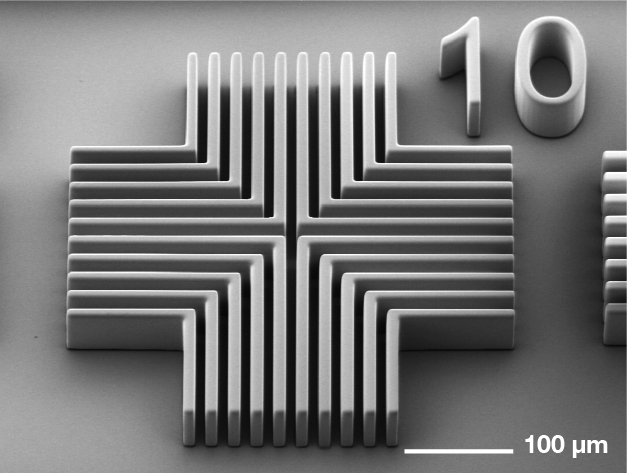

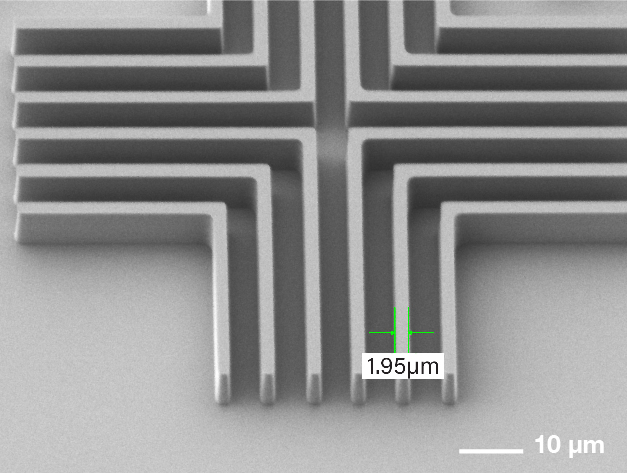

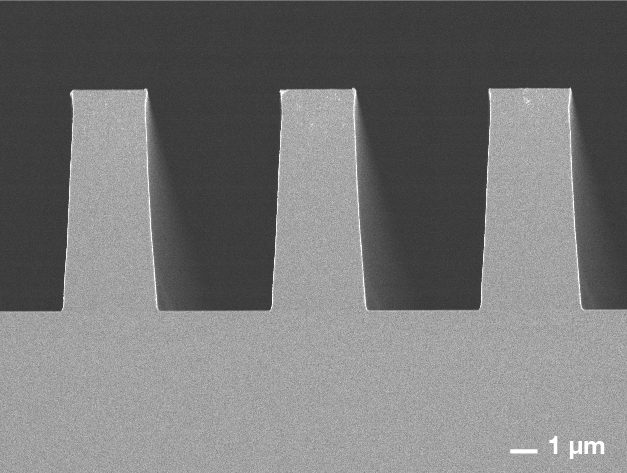

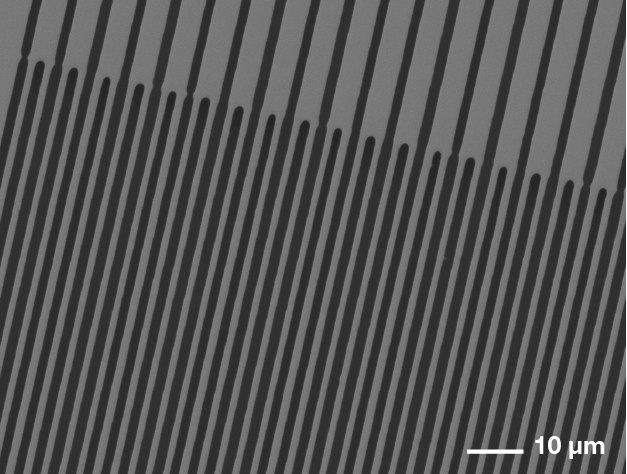

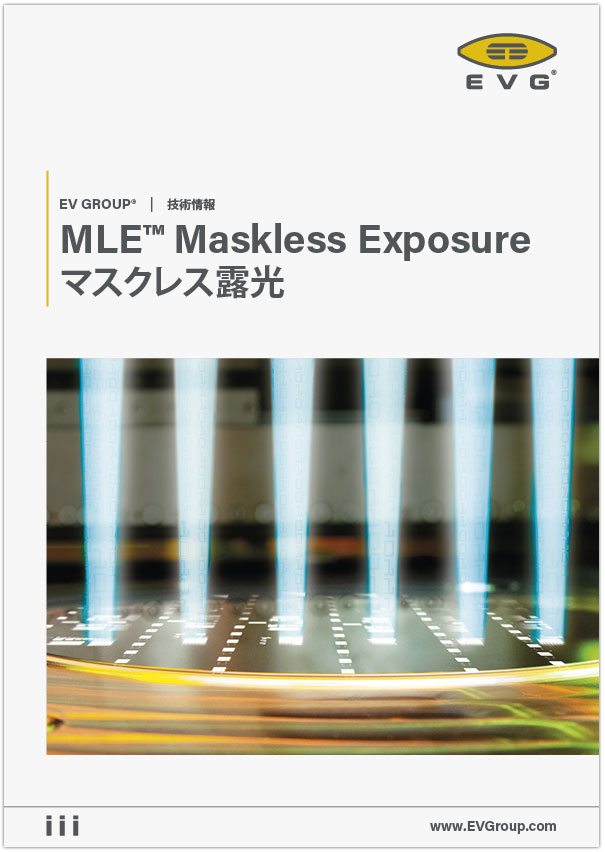

EVGのMLE技術は、基板表面全体への高解像度(<2µm L/S)で繋ぎ目の無いマスクレス露光を、高スループットと低所有コストで実現します。MLEは、研究開発から量産体制への迅速な移行、スループットの最適化、さまざまな基板サイズや材料への適応を可能にするとともに、小型のシリコン/化合物半導体ウェーハからパネルサイズまで、あらゆる基板を処理するために理想的な技術です。 そして、柔軟で拡張性の高い高出力UVレーザー光源によって、多波長露光をオプションで備え、フォトレジストの種類に依存することなく、同様のパター二ング性能を達成します。

EVGは、新たなリソグラフィ装置を市場へ導入するだけでなく、スループット、フォーマット、そして消耗品不要な製造工程基盤を可能にする拡張性の高い独自のマスクレス技術を提供し、半導体業界の高度で迅速なデジタル処理の重要なニーズに対応することを目指しています。

特長

- 全面露光可能でスティッチフリーのダイナミックフォトレジストパター二ング

- 任意方向への2 µm以下のライン/スペース解像度

- デジタルデータでプログラミング可能なレイアウトにより、デザインの自由度とデータの機密性を確保

- 個々のダイへの注釈の露光が可能(シリアルナンバー、暗号キー等)

- ウェーハレベルでのパターン登録とエラー補正

- 基板の変形や反りの影響を受けない(厚いウェーハ、ガラスまたは有機基板など)

- 高性能で敏速なデジタルリソグラフィのプロセッシングインフラストラクチャ

- 消耗品が不要

数値

Related downloads

Related products

Talk to our EVG technology experts!

Questions?

Events

ICEP 2025

Listen to our talks "Wafer Bonding Advances & 3D Applications" held by our Representative Director Hiroshi Yamamoto on 9:30 Wednesday, April 16 / Room B and "Hybrid Bonding for Heterogenous Integration" held by our Process Technology Manager Europe Gerald Mittendorfer on 12:40 Friday, April 18 / Room A.

JFS Conference and Compoundsemiconductor Industry Expo 2025

Visit our booth #A308

MicroNanoFabrication Annual Review Meeting 2025

Visit our booth at the MicroNanoFabrication Annual Review Meeting 2025!

Share this page with your colleagues on LinkedIn

Questions about our technologies?

Contact the EVG experts