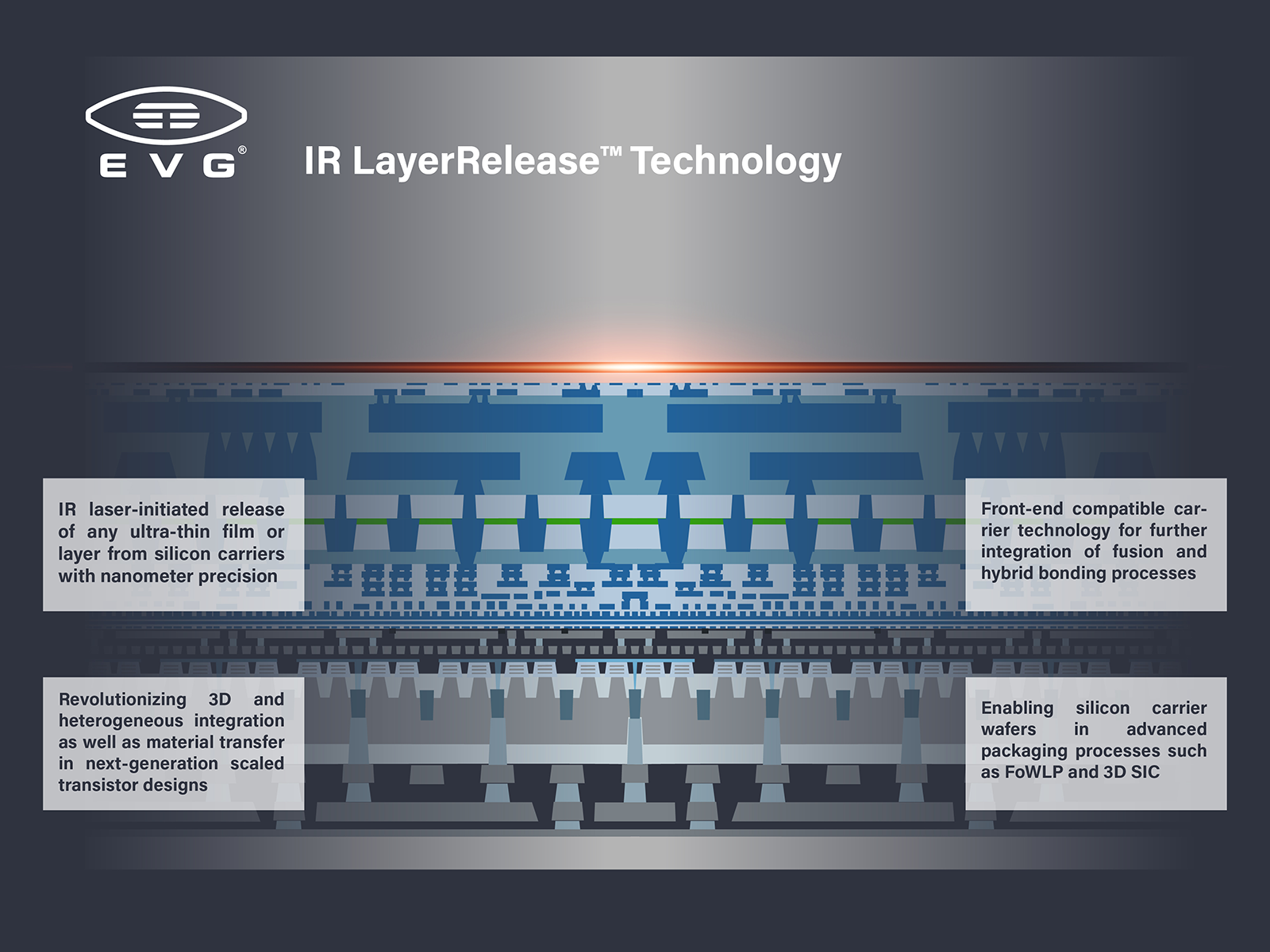

IR LayerRelease™ 技術

IR LayerRelease™ 技術により、シリコンを介したナノメートル精度のレイヤー・トランスファーを実現、ガラス基板を使用しない先端パッケージング向け薄層3次元積層を可能に

イントロダクション

EVGのIR LayerRelease技術は、前工程と完全に整合し、シリコンを通過可能な波長を持つ赤外線(IR)レーザーを用いた層剥離技術です。赤外線レーザーと特殊な無機層を組み合わせることで、シリコン支持基板から任意の超薄膜やレイヤーをナノメートルの精度で剥離します。

IR LayerRelease技術により、モールドと再配列ウェーハを用いたFoWLP(Fan-out Wafer-level Packaging / ファンアウト・ウェーハレベル・パッケージング)や3次元積層IC(3D SIC)用インターポーザーなどの先端パッケージプロセスでシリコン支持基板を使うことが可能になります。同時に、高温プロセスとの親和性により、3D ICや3次元シーケンシャル実装アプリケーションにおいて全く新しいプロセスフローを実現し、シリコン支持基板上の極薄層ともハイブリッド/フュージョン接合が可能となり、次世代微細化トランジスタ構造における3次元・ヘテロ集積や異種材料のトランスファー技術に革新をもたらします。

3次元積層と後工程に有益なシリコン支持基板

益々増大する相互配線の帯域幅に対応した高性能システムを実現するため、薄ウェーハ処理用支持基板の技術は3次元実装において重要な鍵となっています。ガラス支持基板を有機接着剤で仮貼り合わせしたあと、紫外線(UV)波長レーザーを用いて接着剤を分解してデバイス層を剥離し、最終製品のウェーハに永久接合する、という方法は、デバイス層の積層方法として既に確立されています。しかし、シリコン基板を前提に設計された半導体製造装置では、ガラス基板の処理は難しく、これを可能にするためにはその使用に合わせた装置の改造が必要となり、その費用も高額です。また、有機接着剤は一般的に処理温度が300℃以下に制限されるため、後工程での使用に限定されます。

しかし、このような温度の制約やガラス基板との相性の問題は、シリコン支持基板に無機剥離層を施すことで解決できます。また、IRレーザーによる劈開はナノメートル単位の精度であるため、従来のプロセスを変更することなく、極薄デバイスウェーハの処理を可能にします。このような薄いデバイス層を積層することで、より広い帯域幅の相互接続が可能になり、次世代高性能システム向けの設計やセグメント・ダイの新しい可能性が開かれます。

次世代トランジスタ・ノードに求められる新しいレイヤー・トランスファー・プロセス

同時に、サブ3nmノードのトランジスタロードマップでは、埋め込み電源レール、裏面電力供給ネットワーク、相補型電界効果トランジスタ(CFET)、さらには2次元層状チャンネルなどの新しいアーキテクチャや設計上のイノベーションが求められており、これらすべてに極薄材料のレイヤー・トランスファーが必要になってきます。プロセスの清浄度、材料適合性、高温処理など前工程での製造フローに必要とされる要件に、シリコン支持基板と無機剥離層は対応します。しかし従来、シリコン支持基板は研削、研磨、エッチングなどの工程で完全に除去する必要があったため、デバイス動作層の表面にミクロン単位のばらつきが生じてしまい、先端ノードでの薄層積層には不向きな方法であるとされてきました。

EVGの新技術は、赤外線レーザーと無機の剥離材料を利用し、シリコン基板上でのレーザー剥離をナノメートル精度で可能にするものです。これにより、先端パッケージング向けのガラス基板が不要となり、温度の制限やガラス支持基板との相性の問題を解決できるほか、従来のプロセスを変更することなく、支持基板を介した極薄(シングルミクロン以下)層のトランスファーを前工程で行うことができるようになります。EVGの新しいプロセスはナノメートルの精度を誇り、デバイス層やパッケージの薄化が必要とされる先端半導体デバイスのロードマップをサポートし、ヘテロ集積化の普及を加速するだけでなく、薄層トランスファーの採用や高価なガラス基板を使わないことによるプロセスコストの削減を可能にします。

EVGのIR LayerRelease技術では、シリコンを透過する独自の波長を利用した赤外レーザーをシリコンウェーハの裏面側から照射します。標準的な成膜プロセスによってシリコンスタックにあらかじめ形成された無機剥離層が赤外光を吸収し、その結果、正確に所定の層または領域でシリコンが劈開されます。無機剥離層を使用することで、より精密かつ薄く(有機接着剤の数ミクロンに対して数ナノメートル)剥離層を制御することができます。さらに、無機剥離層は高温プロセス(1000℃まで)に適合するため、有機接着剤が使用できなかったエピタキシャル成長、成膜、アニールなど多くの新しい前工程のアプリケーションでレイヤー・トランスファーが可能になります。

特長

- 3D積層|スケーリングロードマップ:

- メスのような精度のIRレーザーでシリコンウェーハを透過し、層を剥離

- フュージョン/ハイブリッド接合による超薄膜積層のための、画期的な3次元積層プロセスフローを実現

- ハイブリッド接合やフュージョン接合の組み合わせで、高度なデバイス製造と3次元積層を実現

- 既存のFEOL材料、プロセス、インフラを使用

- 剥離層の均一性はエピタキシーの制御精度によって定義される為、標準的なウェーハ研削、研磨、エッチングによるウェーハ薄化に於ける均一性の制限を排除

- III-Vs、2D材料、超格子などのフュージョン接合と組み合わせたユニバーサルな異種材料のトランスファー

- ヘテロジニアス・インテグレーション:

- シリコン支持基板を暫定支持基板として使用可能

- 支持基板材料に由来する温度制限の排除。低温でプロセスを行う必要なく、標準的で確立されたプロセス技術の使用が可能。

- 最先端リソグラフィー手法を使用したシリコン基板上での超微細ピッチ再配線層パターニングの処理が可能

- ガラスウェーハを使用する事によって発生する高額な装置の更新・改造や裏面の成膜が不要

Related downloads

Related products

Talk to our EVG technology experts!

Questions?

Events

ECTC 2025

Visit our booth #330 and our PDC "Wafer-to-Wafer and Die-to-Wafer Hybrid Bonding for Advanced Interconnects" held by Dr. Viorel Dragoi on 27th of May and listen as well to our talks “Advanced FO PLP Digital Lithography Patterning Development for AI Devices” & “Wafer-to-Wafer Bonding With Saddle-Shaped Wafers” held by Dr. Ksenija Varga and Anton Alexeev on 29th of May. We are also looking forward to meet you at the poster session on 29th of May where Urban Peter will present “IR Laser Debonding for Silicon Based Temporary Carrier Systems Enabling 2.5D and 3D Chiplet Integration Processes”

MicroNanoFabrication Annual Review Meeting 2025

Visit our booth at the MicroNanoFabrication Annual Review Meeting 2025!

JFS Conference and Compoundsemiconductor Industry Expo 2025

Visit our booth #A308

Share this page with your colleagues on LinkedIn

Questions about our technologies?

Contact the EVG experts